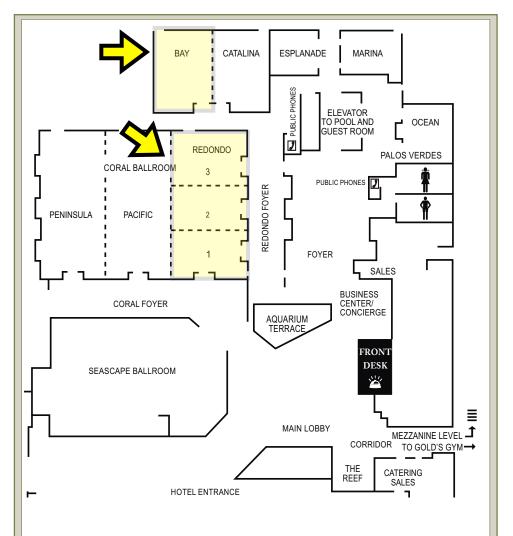

#### MEETING ROOMS

The meeting rooms are Bay Room and Redondo Room. The plenary sessions are held in Redondo Room.

# ISLPED'12

CROWNE PLAZA HOTEL REDONDO BEACH, CA

July 30-Aug. 1, 2012

(RECEPTION SUNDAY EVENING)

#### SUNDAY, JULY 29, 2012 TIME **BAY ROOM** REDONDO ROOM 18:00 Reception MONDAY, JULY 30, 2012 7:00 Breakfast 8:00 Chairs' Welcome 8:30 Keynote by Pradip Bose, IBM "Energy Secure Computing" 9:30 Break 10:00 Session 2: Tools for Session 1: Circuits Physical Design in Emerging and Architecture **Techniques** Simulation 11:30 Lunch 13:00 Session 3: Caches, Session 4: Industry Memories, and FOcus Session on Interconnect Low Power Design 15:00 Break 15:30 Session 6: System Session 5: Low Level Power Power SRAM Optimization 17:00 Session 7: Panel -Session 8: Low Going Green Power Design and Across Validation Communication Methodologies and Storage Subsystems 18:30 (free activity)

## ISLPED 2012 Program at a Glance

| Tuesday, July 31, 2012 |                                                                                                              |                                                                                                             |

|------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Тіме                   | TIME BAY ROOM REDONDO ROOM                                                                                   |                                                                                                             |

| 7:00                   | Brea                                                                                                         | kfast                                                                                                       |

| 8:00                   | Keynote by Kaushik Roy, Purdue U.<br>"Spin as State Variable for Computation:<br>Prospects and Perspectives" |                                                                                                             |

| 9:00                   | Bre                                                                                                          | eak                                                                                                         |

| 9:30                   | Session 9: Digital<br>Techniques                                                                             | Session 10: Energy<br>Efficiency and Non-<br>Volatile Memories                                              |

| 11:30                  | Poster Session                                                                                               |                                                                                                             |

| 12:00                  | Lunch                                                                                                        |                                                                                                             |

| 13:30                  | Session 11:<br>Innovations in Low<br>Power Analog                                                            | Session 12:<br>Software-Driven<br>Techniques for<br>Energy Efficiency in<br>Embedded Multi-<br>Core Systems |

| 15:30                  | Break                                                                                                        |                                                                                                             |

| 16:00                  | Design Contest                                                                                               | Embedded Tutorial                                                                                           |

| 17:30                  | Industry Reception                                                                                           |                                                                                                             |

| 19:00                  | Social Event - Banquet                                                                                       |                                                                                                             |

| W     | WEDNESDAY, AUGUST 1, 2012                                                                          |                                                       |  |

|-------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Тіме  | BAY ROOM                                                                                           | REDONDO ROOM                                          |  |

| 7:30  | Breakfast                                                                                          |                                                       |  |

| 8:30  | Keynote by Uming Ko, MediaTek USA,<br>"Ultra-Low Power Challenges for the Next<br>Generation ASIC" |                                                       |  |

| 9:30  | Break                                                                                              |                                                       |  |

| 10:00 | Session 13:<br>Processor Design<br>and Implementation                                              | Session 14:<br>Memory<br>Management and<br>Scheduling |  |

#### Monday, July 30, 2012 (1/2)

| TIME                | BAY ROOM                                                                                                                                                              | REDONDO ROOM                                                                                                                                    |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:00                | Breakfa                                                                                                                                                               | ast                                                                                                                                             |

| 8:00                | Chairs' Welcome (Bay Room)                                                                                                                                            |                                                                                                                                                 |

| 8:30                | Keynote: Energy Secure Computing - Speaker: Pradip Bose, IBM<br>Chair: Massimo Poncino, Politecnico di Torino                                                         |                                                                                                                                                 |

| 9:30                | Brea                                                                                                                                                                  | k                                                                                                                                               |

| 10:00<br>-<br>11:30 | Session 1: Circuits in Emerging<br>Techniques<br>Chair: Kangho Lee (Qualcomm), Co-<br>Chair: Jae-Joon Kim (IBM)                                                       | Session 2: Tools for Physical<br>Design and Architecture<br>Simulation<br>Chair: Houman Homayoun (George<br>Mason U)                            |

| 10:00               | ★ Write-Optimized Reliable Design of<br>STT MRAM<br>Yusung Kim, Sumeet Gupta, Sang Phill<br>Park, Georgios Panagopoulos, Kaushik<br>Roy (Purdue U)                    | Practically Scalable Floorplanning<br>with Voltage Island Generation<br>Song Chen, Xiaolin Zhang, Takeshi<br>Yoshimura (Waseda U)               |

| 10:30               | High-Performance Low-Energy STT<br>MRAM Based on Balanced Write<br>Scheme<br>Dongsoo Lee, Sumeet Gupta, Kaushik<br>Roy (Purdue U)                                     | ★ TSV Array Utilization in Low-<br>Power 3D Clock Network Design<br>Xin Zhao, Sung Kyu Lim (Georgia<br>Institute of Technology)                 |

| 11:00               | Design Benchmarking to 7nm with<br>FinFET Predictive Technology Models<br>Saurabh Sinha, Brian Cline, Greg Yeric,<br>Vikas Chandra (ARM); Yu Cao (Arizona<br>State U) | Thermal-Aware Sampling in<br>Architectural Simulation<br>Ehsan K. Ardestani, Elnaz Ebrahimi,<br>Gabriel Southern, Jose Renau (UC<br>Santa Cruz) |

| 11:30               | Lunch                                                                                                                                                                 |                                                                                                                                                 |

| 13:00<br>-<br>15:00 | Session 3: Caches, Memories, and Interconnect<br>Chair: Saurabh Sinha (ARM), Co-Chair: Xiangyu Dong (Qualcomm)                                                        | Session 4: Industry Focus<br>Session on Low Power Design<br>Chair: Clive Bittlestone (Texas<br>Instruments)                                     |

| Тіме                | BAY ROOM                                                                                                                                                                                                                                                                | REDONDO ROOM                                                                                                                              |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 13:00               | ★ ER: Elastic RESET for Low Power and<br>Long Endurance MLC based Phase<br>Change Memory<br>Lei Jiang, Youtao Zhang, Jun Yang (U of<br>Pittsburgh)                                                                                                                      | Advances in Ultrabook™ Platform<br>Power Management<br>Jim Kardach (Intel Corp.)                                                          |

| 13:30               | A Dual-mode Architecture for Fast-<br>switching STT-RAM<br>Zhenyu Sun, Hai (Helen) Li (Polytechnic<br>Institute of New York U); Wenqing Wu<br>(Qualcomm Inc)                                                                                                            | Commercial Low-Power EDA Tools:<br>A Review<br>Renu Mehra (Synopsys)                                                                      |

| 14:00               | ASCIB: Adaptive Selection of Cache Indexing Bits for Removing Conflict Misses Alberto Ros (Universidad de Murcia); Polychronis Xekalakis (Intel Labs Barcelona); Marcelo Cintra (The University of Edinburgh); Manuel E. Acacio, José M. García (Universidad de Murcia) | An ARM perspective on Addressing<br>Low-Power Energy-Efficient SoC<br>Designs<br>David Flynn (ARM)                                        |

| 14:30               | Energy Efficient Non-Minimal Path On-<br>chip Interconnection Network for<br>Heterogeneous Systems<br>Jieming Yin, Pingqiang Zhou, Anup<br>Holey, Sachin S. Sapatnekar, Antonia<br>Zhai (U of Minnesota, Twin Cities)                                                   | Panel  Moderator: Ajith Amerasekera (TI)  Panelists: Barry Pangrle (Mentor), Jim Kardach (Intel); RenuMehra (Synopsys), David Flynn (ARM) |

| 15:00               | Brea                                                                                                                                                                                                                                                                    | k                                                                                                                                         |

| 15:30<br>-<br>17:00 | Session 5: Low Power SRAM  Chair: Min Huang (Intel), Co-Chair: Srini Sridhara (Texas Instruments)                                                                                                                                                                       | Session 6: System Level Power<br>Optimization  Chair: Yung-Hsiang Lu (Purdue), Co-<br>Chair: Ayse K. Coskun (Boston<br>Univ.)             |

### Monday, July 30, 2012 (2/2)

| Тіме                | BAY ROOM                                                                                                                                                                                                                                                                                                           | REDONDO ROOM                                                                                                                                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:30               | A 55nm 0.55V 6T SRAM with Variation-<br>Tolerant Dual-Tracking Word-Line Under-<br>Drive and Data-Aware Write-Assist<br>Yi-Wei Lin, Hao-I Yang, Geng-Cing Lin,<br>Chi-Shin Chang, Ching-Te Chuang, Wei<br>Hwang (National Chiao Tung U); Chia-<br>Cheng Chen, Willis Shih, Huan-Shun<br>Huang (Faraday Technology) | Power-aware Performance Increase<br>via Core/Uncore Reinforcement<br>Control for Chip-Multiprocessors<br>Da-Cheng Juan, Diana Marculescu<br>(CMU)                                                                         |

| 16:00               | A 40-nm 256-Kb Sub-10 pJ/Access 8T SRAM with Read Bitline Amplitude Limiting (RBAL) Scheme Shusuke Yoshimoto, Masaharu Terada, Youhei Umeki, Shunsuke Okumura (Kobe University); Atsushi Kawasumi, Toshikazu Suzuki, Shinichi Moriwaki, Shinji Miyano (STARC); Hiroshi Kawaguchi, Masahiko Yoshimoto (Kobe U)      | Power Conversion Efficiency<br>Characterization and Optimization for<br>Smartphones<br>Woojoo Lee, Yanzhi Wang (U of<br>Southern California); Donghwa Shin,<br>Naehyuck Chang (Seoul National U);<br>Massoud Pedram (USC) |

| 16:30               | An Adaptive Write Word-Line Pulse Width and Voltage Modulation Architecture for                                                                                                                                                                                                                                    | Dynamic Reconfiguration of<br>Photovoltaic Energy Harvesting<br>System in Hybrid Electric Vehicles<br>Yanzhi Wang, Xue Lin (USC);<br>Naehyuck Chang (Seoul National U);<br>Massoud Pedram (USC)                           |

|                     | Bit-Interleaved 8T SRAMs Daeyeon Kim (U of Michigan); Vikas Chandra, Robert Aitken (ARM); David Blaauw, Dennis Sylvester (U of Michigan)                                                                                                                                                                           | Battery Management for Grid-<br>connected PV Systems with a<br>Battery<br>Sangyoung Park (SNU); Yanzhi<br>Wang (USC); Younghyun Kim,<br>Naehyuck Chang (SNU); Massoud<br>Pedram (USC)                                     |

| 17:00<br>-<br>18:30 | Session 8: Low Power Design and<br>Validation Methodologies<br>Chair: Michael Orshansky (UT Autin)                                                                                                                                                                                                                 | Session 7: Panel - Going Green<br>Across Communication and<br>Storage Subsystems<br>Session Chair: Ken Wagner (PMC-<br>Sierra, Inc)                                                                                       |

| TIME  | BAY ROOM                                                                                                                                                                                                                                                     | REDONDO ROOM                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:00 | Modeling, Design and Cross-Layer<br>Optimization of Polysilicon Solar Cell<br>Based Micro-scale Energy Harvesting<br>System<br>Elif Selin Mungan, Chao Lu, Kaushik<br>Roy, Vijay Raghunathan (Purdue U)                                                      | Panelists:  Martin St. Laurent (Qualcomm, USA) Robert Aitken (ARM, USA) Hugh Barrass (Cisco, USA) Randall Robinson (Rackforce Networks, Canada) |

| 17:30 | Static Low Power Verification Flow at<br>Transistor Level for SoC Design<br>Jérôme Lescot, Vincent Bligny<br>(STEricsson); Dina Medhat (Mentor<br>Graphics); Didier Chollat-Namy<br>(STEricsson); Ziyang Lu, Sophie Billy,<br>Mark Hofmann (Mentor Graphics) | (panel continued)                                                                                                                               |

| 18:00 | CCP: Common Case Promotion for<br>Improved Timing Error Resilience with<br>Energy Efficiency<br>Lu Wan, Deming Chen (University of<br>Illinois at Urbana-Champaign)                                                                                          | (panel continued)                                                                                                                               |

|       | Energy-Optimal Caches with Guaranteed Lifetime Mirko Loghi (University di Udine); Haroon Mahmood, Andrea Calimera, Massimo Poncino, Enrico Macii (Politecnico di Torino)                                                                                     |                                                                                                                                                 |

| 18:30 | (Free Activity)                                                                                                                                                                                                                                              |                                                                                                                                                 |

### Tuesday, July 31, 2012 (1/3)

| TIME            | BAY ROOM                                                                                                                                                                       | REDONDO ROOM                                                                                                                                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:00            | Breakfast                                                                                                                                                                      |                                                                                                                                                                                                                              |

| 8:00            | Keynote: Spin as State Variable for Computation: Prospects and Perspectives Speaker: Kaushik Roy, Purdue University Chair: Naresh Shanbhag, UIUC                               |                                                                                                                                                                                                                              |

| 9:00            | Bre                                                                                                                                                                            | ak                                                                                                                                                                                                                           |

| 9:30 -<br>11:30 | Session 9: Digital Techniques<br>Chair: Nikola Nedovic (Fujitsu), Co-<br>Chair: Steven Bartling (Texas<br>Instruments)                                                         | Session 10: Energy Efficiency and<br>Non-Volatile Memories<br>Chair: Elaheh Bozorgzadeh (UC<br>Irvine), Co-Chair: John Sartori (UMN)                                                                                         |

| 9:30            | Register File Write Data Gating<br>Techniques and Break-Even Analysis<br>Model<br>Eric Donkoh, Teck Siong Ong, Yan Nee<br>Too (Intel Corp); Patrick Chiang<br>(Oregon State U) | Improving Energy Efficiency of Write-<br>Asymmetric Memories by Log Style<br>Write<br>Guangyu Sun (Peking U.); Yaojun<br>Zhang (UPitt), Yu Wang (Tsinghua U.);<br>Yiran Chen (UPitt)                                         |

| 10:00           | A Low-Leakage Dynamic Register File<br>with Unclocked Wordline and Sub-<br>Segmentation for Improved Bitline<br>Scalability<br>Eric Donkoh (Intel); Patrick Chiang<br>(OSU)    | Process Variation Aware Data<br>Management for STT-RAM Cache<br>Design<br>Zhenyu Sun, Xiuyuan Bi, Hai (Helen)<br>Li (Polytechnic Institute of New York<br>U)                                                                 |

| 10:30           | A Fine-Grained Many V⊤ Design<br>Methodology for Ultra Low Voltage<br>Operations<br>Mingoo Seok (Columbia U)                                                                   | ★ TapeCache: A High Density, Energy Efficient Cache Based on Domain Wall Memory. Rangharajan Venkatesan, Vivek Kozhikkottu (Purdue); Charles Augustine, Arijit Raychowdhury (Intel); Kaushik Roy, Anand Raghunathan (Purdue) |

| 11:00           | A Programmable Resistive Power Grid<br>for Post-Fabrication Flexibility and<br>Energy Tradeoffs<br>Kyle Craig (U of Virginia & AMD),                                           | A Software Approach for Combating<br>Asymmetries of Non-Volatile<br>Memories<br>Yong Li, Yiran Chen, Alex K. Jones<br>(UPitt)                                                                                                |

|                 | Yousef Shakhsheer, Sudhanshu<br>Khanna, Saad Arrabi, John Lach,<br>Benton Calhoun (U of Virginia);<br>Stephen Kosonocky (Advanced Micro<br>Devices)                            | Design of Low Power 3D Hybrid<br>Memory by Non-volatile CBRAM-<br>Crossbar with Block-level Data-<br>retention<br>Yuhao Wang, Chun Zhang, Hao Yu,<br>Wei Zhang (Nanyang Tech. U)                                             |

| TIME  | BAY ROOM                                                                                                                                                              | REDONDO ROOM                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 11:30 | Poster S<br>Chair: Antonia Zhai (Univ. of Minnesota),                                                                                                                 |                                        |

|       | TAP: Token-Based Adaptive Power Gating Tajana Rosing, Richard Strong (UCSD)                                                                                           | . Andrew Kahng, Seokhyeong Kang,       |

|       | Design Trade-Offs for High Density Cross-Point Resistive Memory. Dimin Niu, Cong Xu (Penn State Univ.); Naveen Muralimanohar, Norman Jouppi (HP Labs); Yuan Xie (PSU) |                                        |

|       | Performance and Energy-Efficiency Impro<br>Transistor Integrated Circuits. Mingoo Seo                                                                                 |                                        |

|       | Optimal Power Switch Design for Dynamic to Subthreshold Operation. Kyle Craig, You Virginia)                                                                          |                                        |

|       | BiN: A Buffer-in-NUCA Scheme for Accelerator-Rich CMPs. Jason Cong,<br>Mohammad Ali Ghodrat, Michael Gill, Chunyue Liu, Glenn Reinman (UCLA)                          |                                        |

|       | Adopting TLB Index-based Tagging to Data<br>Jongmin Lee, Soontae Kim (KAIST)                                                                                          | a Caches for Tag Energy Reduction.     |

|       | Static and Dynamic Co-Optimizations for E<br>Ting Chen, Jason Cong, Hui Huang, Chun<br>Reinman (UCLA)                                                                 | ,, ,                                   |

|       | Design Space Exploration of Workload-sp<br>Swaminathan, Emre Kultursay, Vinay Sari<br>Kandemir (Penn. State U.)                                                       |                                        |

|       | Low-Power Adaptive RF Systems using Re<br>Debashis Banerjee (Georgia Institute of Te<br>Banerjee, Abhijit Chatterjee (Georgia Tech                                    | chnology); Shreyas Sen (Intel); Aritra |

|       | Designing for Dark Silicon: A Methodologic<br>Systems. Jason Allred, Sanghamitra Roy,                                                                                 |                                        |

|       | HANDS: Heterogeneous Architectures and Simulation. Davide Zoni, Simone Corbetta Milano)                                                                               |                                        |

<sup>★</sup> best-paper candidate

#### Tuesday, July 31, 2012 (2/3)

| ТІМЕ                | BAY ROOM                                                                                                                                                                                                                                   | REDONDO ROOM                                                                                                                                                   |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     | XIOSim: Power-Performance Modeling of Mobile x86 Cores. Svilen Kanev, Gu-<br>Yeon Wei, David Brooks (Harvard U.)                                                                                                                           |                                                                                                                                                                |  |

|                     | LogStore: Toward Energy-Proportional Sto<br>Centeno (Rutgers U.); Frederic Chong (UC                                                                                                                                                       | orage Servers. Wei Zheng, Ana Paula<br>CSB); Ricardo Bianchini (Rutgers U.)                                                                                    |  |

|                     | A Game Theoretic Resource Allocation for Overall Energy Minimization in Mobile Cloud Computing System. Yang Ge, Yukan Zhang, Qinru Qiu (Syracuse U.); Yung-Hsiang Lu (Purdue U.)                                                           |                                                                                                                                                                |  |

|                     | A Low-power "Near-threshold" Epileptic Seizure Detection Processor with Multiple Algorithm Programmability. Himanshu Markandeya (Purdue U.); Shriram Raghunathan (Cyberonics Inc.); Pedro Irazoqui, Kaushik Roy (Purdue U.)                |                                                                                                                                                                |  |

|                     | Understanding the Impact of Laptop Power Saving Options on User Satisfaction Using Physiological Sensors. Matthew Schuchhardt, Ben Scholbrock, Utku Pamuksuz, Gokhan Memik, Peter Dinda (Northwestern U.); Robert P. Dick (U. of Michigan) |                                                                                                                                                                |  |

|                     | MultiScale: Memory System DVFS with Multiple Memory Controllers. Qingyuan Deng (Rutgers U.), David Meisner (Facebook), Abhishek Bhattacharjee (Rutgers), Thomas F. Wenisch (UMich), Ricardo Bianchini (Rutgers)                            |                                                                                                                                                                |  |

|                     | Semantics-driven Sensor Configuration for Energy Reduction in Medical Sensor Networks James B. Wendt, Saro Meguerdichian, Hyduke Noshadi, Miodrag Potkonjak (UCLA)                                                                         |                                                                                                                                                                |  |

| 12:00               | Lunch                                                                                                                                                                                                                                      |                                                                                                                                                                |  |

| 13:30<br>-<br>15:30 | Session 11: Innovations in Low<br>Power Analog<br>Chair: Rajeevan Amirtharajah (UC<br>Davis), Co-Chair: Karthik Kadirvel<br>(Texas Instruments)                                                                                            | Session 12: Software-Driven Techniques for Energy Efficiency in Embedded and Multi-Core Systems Chair: Nikil Dutt (UC Irvine), Co- Chair: Vivek Tiwari (Intel) |  |

| TIME  | BAY ROOM                                                                                                                                                                                                                                                                  | REDONDO ROOM                                                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:30 | Voltage Droop Reduction for Multiple-<br>Power Domain SoCs with On-Die LDO<br>Using Output Voltage Boost and<br>Adaptive Response Scaling<br>Tetsutaro Hashimoto, Satoshi Tanabe,<br>Kouichi Nakayama, Hisanori Fujisawa<br>(Fujitsu Laboratories Limited)                | A Study of the Effectiveness of CPU<br>Consolidation in a Virtualized Multi-<br>Core Server System<br>Inkwon Hwang, Massoud Pedram<br>(USC); Timothy Kam (Intel)                                     |

| 14:00 | ★ A 33µW 42 GOPS/W 64x64 Pixels Vision Sensor with Dynamic Background Subtraction for Scene Interpretation Nicola Cottini, Massimo Gottardi, Nicola Massari (Fondazione Bruno Kessler); Roberto Passerone (Università di Trento); Zeev Smilansky (Emza Visual Sense Ltd.) | Energy-Efficient Scheduling on<br>Heterogeneous Multi-Core<br>Architectures<br>Jason Cong, Bo Yuan (UCLA)                                                                                            |

| 14:30 | Process and Temperature Invariant Bandwidth and Gain, Low-Area, Low-Power and High Swing G <sub>m</sub> -C Filter for Multichannel Neuro-potential Signal Conditioning Anvesha Amaravati, Maryam Shojaei Baghini (IIT-Bombay)                                             | ★ MAC: Migration-Aware Compilation<br>for STT-RAM based Hybrid Cache in<br>Embedded Systems<br>Qingan Li, Jianhua Li, Liang Shi, Chun<br>Jason Xue (City U. of Hong Kong);<br>Yanxiang He (Wuhan U.) |

| 15:00 | A Charge Pump Based Receiver Circuit<br>for a Voltage Scaled Interconnect<br>Aatmesh Shrivastava, John Lach,<br>Benton Calhoun (U. of Virginia)                                                                                                                           | Energy-Efficient Signal Processing in<br>Wearable Embedded Systems: An                                                                                                                               |

|       | 0.35V, 4.1µW, 39MHz Crystal Oscillator Circuit in 40nm CMOS Akira Saito (STARC); Yunfei Zheng (U. of Tokyo); Kazunori Watanabe (STARC); Takayasu Sakurai, Makoto Takamiya (U. of Tokyo)                                                                                   | Optimal Feature Selection Approach Hassan Ghasemzadeh, Navid Amini, Majid Sarrafzadeh (UCLA)                                                                                                         |

| 15:30 | Break                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| 16:00 | Design Contest<br>Co-Chairs: Chia-Lin Yang (National<br>Taiwan U), Yiran Chen (U. of<br>Pittsburgh)                                                                                                                                                                       | Embedded Tutorial: Advanced Power and Thermal Management for Low-Power, High-Performance Smartphones Speaker: Hwisung Jung (Broadcom)                                                                |

## Tuesday, July 31, 2012 (3/3)

| TIME  | BAY ROOM                                                                                                                                                                                                                                                                                | REDONDO ROOM |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|       | An Ultra Energy Efficient Nonvolatile<br>Processor for Self-powered<br>Sensor Platforms. Yiqun Wang,<br>Yongpan Liu, Shuangchen Li, Daming<br>Zhang, Hongyang Jia, Huazhong<br>Yang, Mei-fang Chiang, Yan-xin Yan<br>and Baiko Sai (Tsinghua University)                                |              |

|       | A 14.5 fJ/cycle/k-gate ECG Processor<br>in 45 nm CMOS Using Statistical Error<br>Compensation. Rami Abdallah and<br>Naresh Shanbhag (UIUC)                                                                                                                                              |              |

|       | First-Generation Hybrid Electrical<br>Energy Storage System.<br>Younghyun Kim, Donghwa Shin,<br>Jaehyun Park, Youngil Kim, Jaemin<br>Kim,<br>Sangyoung Park, Kitae Kim(Seoul<br>National University), Massoud Pedram<br>(University of Southern California) and<br>Naehyuck Chang (SNU) |              |

|       | An Embedded Flash Memory in a<br>Generic 65nm Logic Process for Zero-<br>Standby-Power System-on-Chip<br>Applications<br>Seung-Hwan Song, Ki Chul Chun and<br>Chris H. Kim (University of Minnesota)                                                                                    |              |

| 17:30 | Industry Reception                                                                                                                                                                                                                                                                      |              |

| TIME  | BAY ROOM    | REDONDO ROOM |

|-------|-------------|--------------|

| 19:00 | Social Even | it - Banquet |

### Wednesday, August 1, 2012

| ТІМЕ                | BAY ROOM                                                                                                                                                                | REDONDO ROOM                                                                                                                                                                                                                                |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:30                | Breakfast                                                                                                                                                               |                                                                                                                                                                                                                                             |

| 8:30                | <b>Keynote:</b> Ultra-Low Power Challenges for the Next Generation ASIC Speaker: Uming Ko, MediaTek USA Chair: Ajith Amerasekera (Texas Instruments)                    |                                                                                                                                                                                                                                             |

| 9:30                | Break                                                                                                                                                                   |                                                                                                                                                                                                                                             |

| 10:00<br>-<br>12:00 | Chair: Lawrence Clark (Arizona State                                                                                                                                    | Session 14: Memory Management<br>and Scheduling<br>Chair: Naehyuck Chang (Seoul<br>National Univ.), Co-Chair: Guangyu<br>Sun (Peking Univ.)                                                                                                 |

| 10:00               | The Core-C6 (CC6) Sleep State of the AMD Bobcat x86 Microprocessor Aaron Rogers, David Kaplan, Eric Quinnell, Bill Kwan (AMD Austin)                                    | Reducing L1 Caches Power By<br>Exploiting Software Semantics<br>Zhen Fang (NVIDIA); Li Zhao,<br>Xiaowei Jiang, Shin-lien Lu, Ravi<br>Iyer, Tong Li (Intel Corp.); Seung Eun<br>Lee (Seoul National University of<br>Science and Technology) |

| 10:30               | Evaluation of Voltage Stacking for<br>Near-Threshold Multicore Computing<br>Sae Kyu Lee, David Brooks, Gu-Yeon<br>Wei (Harvard University)                              | DRAM Power-Aware Rank<br>Scheduling<br>Sukki Kim (LG Electronics), Soontae<br>Kim, Yebin Lee (Korea Advanced<br>Institute Science and Technology)                                                                                           |

| 11:00               | CHARM: A Composable<br>Heterogeneous Accelerator-Rich<br>Microprocessor<br>Jason Cong, Mohammad Ali Ghodrat,<br>Michael Gill, Beayna Grigorian, Glenn<br>Reinman (UCLA) | Energy-Efficient GPU Design with<br>Reconfigurable In-Package Graphics<br>Memory<br>Jishen Zhao (The Pennsylvania State<br>University); Guangyu Sun (Peking<br>University); Gabriel H. Loh (AMD);<br>Yuan Xie (PSU & AMD)                   |

| Тіме  | BAY ROOM                                                                                                                                                                                                                                                | REDONDO ROOM                                                                                                                                                                                                                                                        |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:30 | Something Old and Something New: P-States Can Borrow Microarchitecture Techniques Too Yasuko Eckert (AMD & U. of Wisconsin-Madison), Srilatha Manne, Michael J. Schulte (Advanced Micro Devices); David A. Wood (University of Wisconsin-Madison & AMD) | Fan-Speed-Aware Scheduling of<br>Data Intensive Jobs<br>Christine S. Chan, Yanqin Jin, Yen-<br>Kuan Wu (University of California,<br>San Diego); Kenny Gross, Kalyan<br>Vaidyanathan (Oracle Physical<br>Sciences Research Center); Tajana<br>Šimunić Rosing (UCSD) |

|       |                                                                                                                                                                                                                                                         | Procedure Hopping: a Low Overhead<br>Solution to Mitigate Variability in<br>Shared-L1 Processor Clusters<br>Abbas Rahimi (University of<br>California, San Diego); Luca Benini<br>(Università di Bologna); Rajesh<br>Gupta (UCSD)                                   |